It is touted as the industry’s first bevel deposition solution optimised to address key manufacturing challenges in next-generation logic, 3D NAND and advanced packaging applications

It is touted as the industry’s first bevel deposition solution optimised to address key manufacturing challenges in next-generation logic, 3D NAND and advanced packaging applications  It is touted as the industry’s first bevel deposition solution optimised to address key manufacturing challenges in next-generation logic, 3D NAND and advanced packaging applications

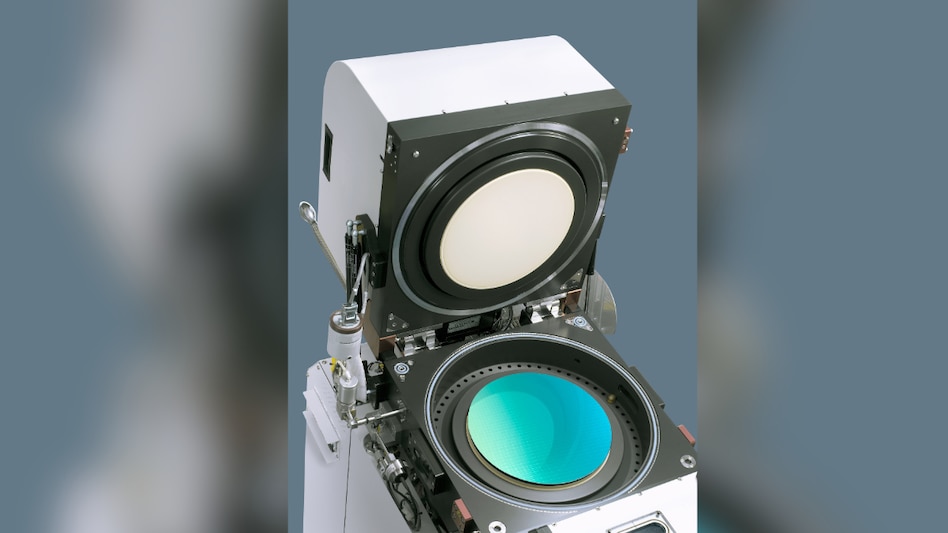

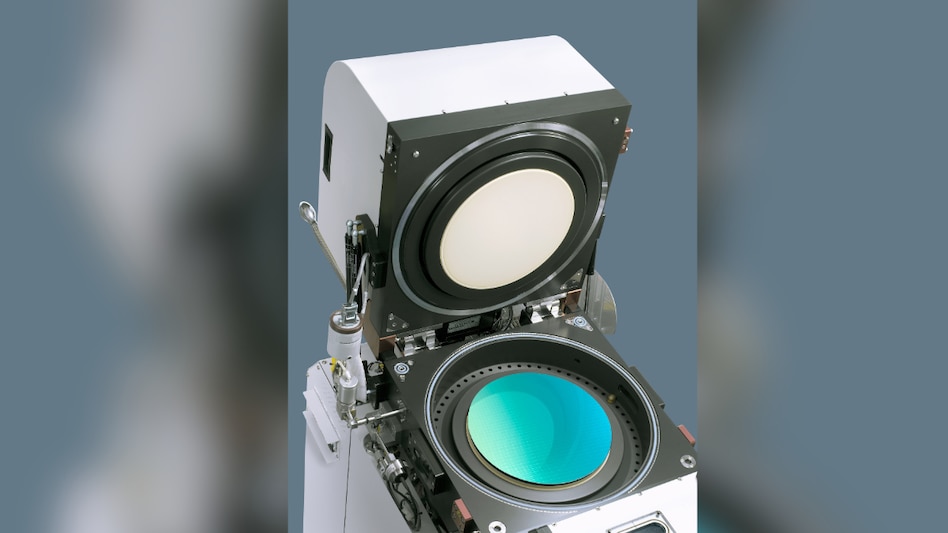

It is touted as the industry’s first bevel deposition solution optimised to address key manufacturing challenges in next-generation logic, 3D NAND and advanced packaging applications With hundreds of processes needed to build nanometer-sized devices on a silicon wafer, manufacturing advanced semiconductors has become increasingly complex. To address this problem, American wafer fabrication equipment manufacturer Lam Research has come up with Coronus DX, which can, in a single step, deposit a proprietary layer of protective film on both sides of the wafer edge that will help prevent defects and damage that can often occur during advanced semiconductor manufacturing.

It is touted as the industry’s first bevel deposition solution optimised to address key manufacturing challenges in next-generation logic, 3D NAND and advanced packaging applications. According to Lam Research, this powerful protection increases yield and enables chipmakers to implement new leading-edge processes for the production of next-generation chips.

“In the era of 3D chipmaking, production is complex and costly,” said Sesha Varadarajan, senior vice present of the Global Products Group at Lam Research. “Building on Lam’s expertise in bevel innovation, Coronus DX helps drive more predictable manufacturing and significantly higher yield, paving the way for adoption of advanced logic, packaging and 3D NAND production processes that weren't previously feasible.”

Coronus DX can enable new device structures. Repeated layers of processing can cause residues and roughness to accumulate along the wafer edge where they may flake off, drift to other areas, and create defects that cause a semiconductor device to fail. For instance, in 3D packaging applications, material from back-end-of-line can migrate and become a contamination source in future processing. Roll-off in the wafer edge profile can impact wafer bonding quality. When those defects cannot be etched away, Coronus DX deposits a thin dielectric layer of protection on the bevel. This precise and tunable deposition helps resolve these common issues that may impact semiconductor quality.

“In a complex manufacturing environment, increasing die yield is critical to maximizing fab productivity” said Rangesh Raghavan, corporate vice president & GM, India at Lam Research. “Close collaboration with our customers is critical in developing innovative solutions like Coronus DX and driving improvement in chipmakers’ production processes.”

First introduced in 2007, the Coronus product line is used by every major semiconductor manufacturer, with several thousand chambers installed globally. Lam’s Coronus product family is the industry’s first mass production-proven bevel technology. Its Coronus and Coronus HP solutions are etch products designed to prevent defects by removing layers along the edge. Coronus solutions are used in the manufacturing of logic, memory and specialty devices, including leading-edge 3D devices. Coronus DX is now being used in high-volume manufacturing at leading customer fabs around the world.

Also Read: India clears Micron’s semiconductor testing and packaging plan

Copyright©2023 Living Media India Limited. For reprint rights: Syndications Today